# Solar PV Array Fed 1-Φ Seven Level Hybrid H-Bridge Inverter For Off-Grid Applications

C. Pavan Kumar<sup>\*1</sup>, Dr. N. Karthick<sup>\*2</sup>, Dr. A. Madhukar Rao<sup>\*3</sup>

\*<sup>1</sup>Research Scholar, Lovely Professional University, Punjab

\*<sup>2</sup>Associate Professor, Lovely Professional University, Punjab

\*<sup>3</sup>Assistant Professor, Kakatiya Institute of Technology and Science, Warangal

## Abstract

Nowadays for high-voltage applications, the Multi-level inverters (MLI) are used extensively and the operation & analysis is easy to that of conventional inverters, because of lower harmonic distortion, switching losses, EMI and lesser number of switches. In conventional MLI, most of the topologies are required more number of switches with High THD and also having more switching losses with voltage equalizing problems. In order to overcome the mentioned drawbacks, the  $1-\varphi$ seven-level Hybrid H-bridge inverter for Off-Grid application with asymmetrical configuration is presented in this work. Further, the DC source voltage is generated by using solar photovoltaic system. The presented inverter topology having six number of switching components, to develop a seven levels across the load from two different ratings of solar PV systems. Further, low frequency pulse width modulation control strategy is utilized for the switching operation of proposed inverter topology presented in this work. The simulation results of the proposed novel seven-level inverter topology is validated with MATLAB/Simulink software tool.

**Keywords**— Multi-Level Inverter (MLI), Low Frequency Pulse Width Modulation (PWM), Asymmetrical Configuration, Total Harmonic Distortion, Solar PV and Off-Grid.

## **INTRODUCTION**

Day to day increment of utilization of electrical energy and for the future generation of electrical energy it should be focused on Non-Conventional energy sources (NCRS). Due to shortage of fossil fuels and without any pollution effect, the NCRS are more predominant in generation of electrical power. Different types of NCRS are available in the nature, but due to the advantages of solar and wind energy sources are more predominant and also pollution free energy sources [1]-[2]. Due to rapid development of power electronic control techniques in electrical power generation and more advantages of solar PV systems, they are used in many industrial and residential applications [3]. The design of PV cells is more demand and popular due to effective use of PV panels [4]. The output of the PV cells are DC Voltage, so if we want to connect to the Grid the power conversion is required [5], for that Inverters are required. In general for industrial application, the voltage Source inverters are effectively utilizing for conversion of energy from dc to ac [6]. But the conventional inverters are having non sinusoidal waveform in nature, with high THD and more switching losses. The fundamental magnitude is also very low [7].

To overcome the above mentioned drawbacks, the multilevel inverters (MLIs) are more attractively developed by researchers in high power and high voltage applications as compared to conventional inverters [8]. It consisting of stepped voltage waveform with low harmonic contents. And increasing the number of voltage levels across the load, it minimizes the total harmonic distortion (THD). For switching operation of the power semiconductor switches in the MLI configuration, pulse width modulation control strategies are introduced to reduce the switching loss. Multi level inverter are having different type of topologies [9], which are Diode Clamped [10], Flying Capacitors [11], Neutral point [12], Cascaded H-Bridge [13]. When compared to all these types of inverters the cascaded Hybrid Multi level Inverter requires a few number of switching devices and also low THD. Generally, in industrial applications, the required number of phases is more. Then the number of switching devices/components increases in cascaded bridge inverter configurations, so the operation is difficult with higher number of switches and conductional losses increase. Which results the inverter will become more complex and costly.

Hybrid multi level inverter topologies are introduced to overcome above mentioned drawbacks with fewer switching devices [14]. The hybrid MLIs are basically consisting two type of configurations, which

are symmetrical and asymmetrical configuration [15]-[16]. To increase the number level with reduced switching count the asymmetrical configuration is best suitable for different rating of PV panels. As compared to different configuration of hybrid inverters the proposed inverter configuration is consisting of lesser switching devices for seven levels. And also the harmonic content is reduced along with its low switching losses and the fundamental component magnitude is increased by using low switching frequency [17]. Further, the module of addition and subtraction of source principle operation based MLI are introduced to overcome the voltage balancing problems across the source side [18]-[19].

The paper is organized as follows. The proposed solar PV fed Hybrid MLI with asymmetrical system configuration is described in section II. In Section III generation of voltage levels across the load for proposed inverter is explained. Switching signal generation of the 7-level Hybrid H-bridge inverter is described in section IV. The MATLAB simulation results of the proposed inverter configuration is analysed in section V. The conclusion of the research work with future scope is mentioned in section VI.

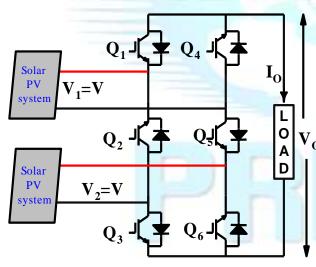

Figure 1 Block diagram Solar PV fed Seven Level Hybrid H-bridge Inverter

## HYBRID H-BRIDGE INVERTER CONFIGURATION

The proposed Solar PV fed 1- $\phi$  Seven- Level Hybrid Hbridge inverter block diagram is shown in Figure 1. The proposed inverter topology consisting six number of power semiconductor switches (IGBT / MOSFET) of Q<sub>1</sub>-Q<sub>6</sub>. And the inverter is fed from the two asymmetrical dc voltage sources; the input dc power is generated by the solar photovoltaic system. In this novel inverter configuration, the two DC voltage sources are connected in series through the IGBT device  $(O_2 \& O_4)$ . The same polarity (positive or negative) /potential (lower or higher) of sources are connected in the same point at the power semiconductor device. And for the generation of seven number of voltage levels across the load, two isolated asymmetrical DC voltages are selected as twice of the other (i.e.V2=2V1). And the entire power semiconductor switches in the configuration are connected in the same way as shown in figure 1, and out of 6 devices 2 devices are connected in opposite direction to remaining switches with series connection for polarity reversal. By using pulse width modulation control strategy, the power semiconductor devices of proposed inverter are turned on and off, then by the addition and subtraction of voltage sources the different voltages levels are produced. The mode of operation of proposed topology explained in section III.

## **MODES OF OPERATIONS**

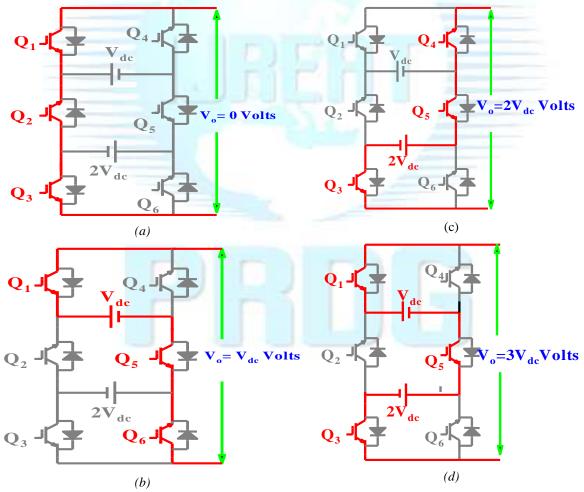

To understand the principle operation of proposed seven-level Hybrid H-bridge inverter, the direction of flow of current from source to load is explained in different modes with generation of different voltage levels. Each mode of operation with active devices appeared in Figure 2. For analysis of switching mode of operations in place of solar PV panel, the DC voltage sources are considered. The eight modes of operations as follows,

*Mode 1*: The combination switches Q1, Q2, and Q3  $V_0$  are enable to activate and remaining switches are deactivated, then the produced load voltage is equal to zero volts. Because of one leg of switches are short circuited. The operation of active circuit with direction of flow of current is appeared in Figure 2(a).

*Mode 2:* The combination switches Q1, Q5 and Q6 are enable to activate and remaining switches are deactivated, and then the produced load voltage is equal to source voltage of V1 volts. The magnitude level of load voltage is equal to  $V_{dc}$ . The operation of active circuit with direction of flow of current is appeared in Figure 2(b).

*Mode 3:* The combination switches Q4, Q5 and Q3 are enable to activate and remaining switches are deactivated, and then the produced load voltage is equal to second source voltage of V2 volts. The magnitude level of load voltage is equal to  $2V_{dc}$ . The operation of active circuit with direction of flow of current is appeared in Figure 2(c).

*Mode 4:* The combination switches Q1, Q5 and Q3 are enable to activate and remaining switches are deactivated, and then the produced load voltage is equal to the addition of two voltage source of V1+V2 volts. The magnitude level of load voltage is equal to  $3V_{dc}$ . The operation of active circuit with direction of flow of current is appeared in Figure 2(d).

*Mode 5:* The combination switches Q4, Q5, and Q6 are enable to activate and remaining switches are deactivated, then the produced load voltage is equal to zero volts. Because of one leg of switches are short circuited. The operation of active circuit with direction of flow of current is appeared in Figure 2(e).

*Mode 6:* The combination switches Q2, Q3 and Q4 are enable to activate and remaining switches are deactivated, and then the produced load voltage is equal to source voltage of V1 volts with opposite polarity. The magnitude level of load voltage is equal to  $-V_{dc}$ . The

operation of active circuit with direction of flow of current is appeared in Figure 2(f).

*Mode 7:* The combination switches Q1, Q2 and Q6 are enable to activate and remaining switches are deactivated, and then the produced load voltage is equal to second source voltage of V2 volts. The magnitude level of load voltage is equal to  $-2V_{dc}$  with opposite polarity. The operation of active circuit with direction of flow of current is appeared in Figure 2(g).

*Mode 8:* The combination switches Q2, Q4 and Q6 are enable to activate and remaining switches are deactivated, and then the produced load voltage is equal to the addition of two voltage source of V1+V2 volts with opposite polarity. The magnitude level of load voltage is equal to  $-3V_{dc}$ . The operation of active circuit with direction of flow of current is appeared in Figure 2(h).

47

Figure . 2 (a)-(h) Different modes of operations of proposed seven level inverter

## SWITCHING SIGNAL TECHNIQUE

For the operation multilevel inverters switching/triggering signals are required for the power semiconductor devices. The switching/triggering signals are generated based on pulse width modulation control strategies. Depends upon the carrier switching frequency the modulation control strategies are classified in to two types, they are low and high switching frequency PWM control strategies/techniques. To reduce the switching losses and harmonic content in the proposed  $1-\phi$  seven-level hybrid H-bridge inverter, low switching frequency modulation control strategy is implemented.

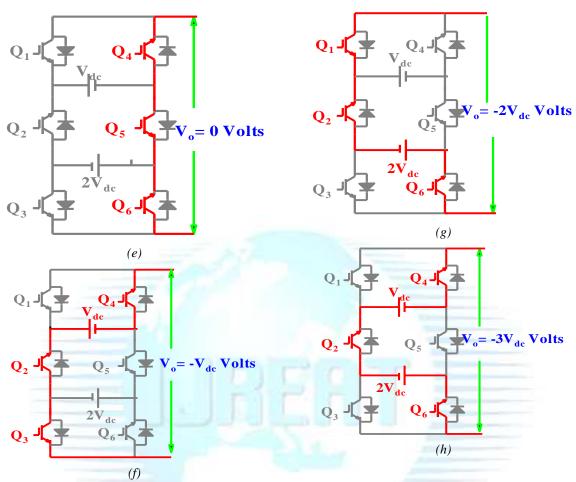

Figure 3 switching sequence of low frequency PWM control scheme

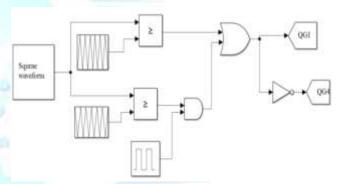

In this presented work, for generation of switching/triggering signals for the proposed hybrid hbridge inverter, a square wave form is used as a reference waveform with fundamental frequency (= 50Hz). The reference waveform is compared with two triangular signals each triangular waveform is phase opposition to other. From the comparison of these signals, two signals G1 & G2 are generated as shown in Figure 3.

Therefore, the required switching/triggering pulses for the power semiconductor switches of Q1 &Q4 of proposed inverter can be generated by using the following mathematical analysis. Similarly, for the Switches signals are generated for Q3 &Q6 with half of the switching frequency of triangle signals used in generation of signals of Q1 & Q4. Table 1 shows that the switching sequence states of all power switches of proposed inverter configuration.

QG1 = G1+G4 G4 = G2\*G3 QG1 = G1+ (G2\*G3) QG4 = QG1'Where (+) stands for logical OR

(\*) stands for logical AND

(') stands for logical NOT.

TABLE I

STATES OF SWITCHING

| s. | Switching operations |                       |                       |            |    |            | Voltage<br>Levels |

|----|----------------------|-----------------------|-----------------------|------------|----|------------|-------------------|

| No | <b>Q</b> 1           | <b>Q</b> <sub>2</sub> | <b>Q</b> <sub>3</sub> | <b>Q</b> 4 | Q5 | <b>Q</b> 6 | 1                 |

| 1  | 1                    | 0                     | 1                     | 0          | 1  | 0          | 3V <sub>dc</sub>  |

| 2  | 0                    | 0                     | 1                     | 1          | 1  | 0          | 2V <sub>dc</sub>  |

| 3  | 1                    | 0                     | 0                     | 0          | 1  | 1          | V <sub>dc</sub>   |

| 4  | 1                    | 1                     | 1                     | 0          | 0  | 0          | 0                 |

| 5  | 0                    | 0                     | 0                     | 1          | 1  | 1          | U                 |

| 6  | 0                    | 1                     | 1                     | 1          | 0  | 0          | -Vdc              |

| 7  | 1                    | 1                     | 0                     | 0          | 0  | 1          | -2V <sub>dc</sub> |

| 8  | 0                    | 1                     | 0                     | 1          | 0  | 1          | -3V <sub>dc</sub> |

#### SIMULATION RESULTS & ANALYSIS

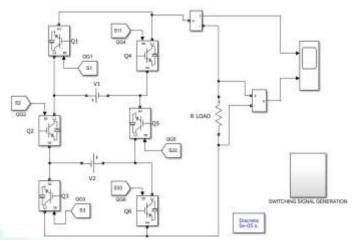

The Solar PV array fed  $1-\varphi$  seven-level hybrid Hbridge inverter configuration shown in Figure 1 has been implemented with MATLAB/Simulink software shown in Figure 4 and performance of the proposed system is analysed is this section. And the switching signal modulation techniques has been explained in section IV, the simulation of the switching signal model as shown in figure 5.

Figure 4 MATLAB/Simulink model of seven-level hybrid H-bridge inverter

Figure 5 MATLAB/Simulink circuit of low frequency PWM technique for generation switching signals for Q1 & Q4

49

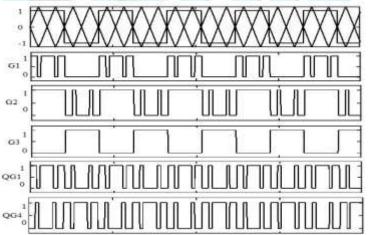

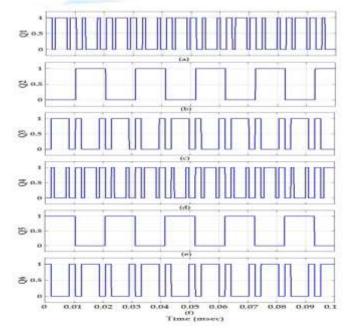

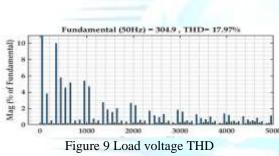

Figure 6 shows the gate triggering signal obtained during simulation of control logic for Hybrid H-Bridge seven-level inverter. Figure 7 and Figure 8 respectively shows that the results of presented single phase sevenlevel inverter load voltage and current simulation waveforms with low frequency pulse width modulation technique.

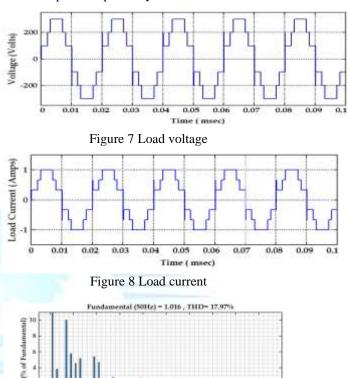

In the Figure 9 & Figure10, FFT analysis of the Hybrid H-bridge seven-level inverter with low frequency PWM scheme is shown. From that it observed, the THD of load voltage is 17.97% with fundamental magnitude of 304.9 volts and THD of load current is 17.97% with fundamental magnitude of

#### **CONCLUSIONS**

In this work, the Solar PV array fed 1-φ seven-level hybrid H-bridge inverter topology has been implemented with MATLAB/Simulink software and performance of the proposed system is analyzed. From the simulation results it was observed that, the performance of presented inverter configuration as improved for Off-Grid application fed solar PV array. In this type of multi-level inverter the output voltage becomes more smooth and sinusoidal with an increase in levels. Then the harmonic content reduces with reduced dv/dt stress. And also the switching losses reduced with improved fundamental component. Moreover, the improved performance of low frequency PWM control strategy seven-level hybrid inverter with reduced harmonic content, the design cost & size of the filters are reduced.

#### FUTURE SCOPE

In this presented work, the seven levels Hybrid Hbridge inverter topology is explained. The fault tolerance ability is very low for the proposed inverter topology. To improve the fault tolerance ability, the novel multi level inverter configuration is to be designed with lesser number switches and THD.

#### 1.016 Amperes respectively for R-Load without filter.

APPENDIX SIMULATION PARAMETERS

Figure 10 Load current THD

| Carrier switching Frequency | F = 100Hz, 50 Hz |

|-----------------------------|------------------|

| DC input voltage            | V= 100 V, 200V   |

| Reference signal frequency  | F=50Hz           |

| Output voltage rating       | 300V             |

| Load Current rating         | 1Amp             |

| Resistive load              |                  |

| R=300ohms                   |                  |

|                             |                  |

#### REFERENCES

- REN21, 2016, "Renewable 2016 Global Status Report," Paris: REN21 Secretariat. ISBN 978-3-9818107-0-7.

- [2] European Commission, "A Vision of Photovoltaic Technology", Directorate-General for Research Sustainable Energy Systems, EUR 21242, 2005.

- [3] Arnulf Jger-Waldau, "PV Status Report 2016," EUR 28159 EN; doi:10.2790/682995.

- [4] E. Romero-Cadaval, G. Spagnuolo, L. G. Franquelo, C. A. Ramos-Paja, T. Suntio, and W. M. Xiao, "Grid-Connected Photovoltaic Generation Plants: Components and Operation,"

*IEEE Industrial Electronics Magazine*, vol. 7, DOI 10/1109/MIE.2013.2264540, no. 3, pp. 6–20, Sep. 2013.

- [5] R.A.Mastromaruo, M.Liserre, and A.Dell' Aquila, "Control issues in single-stage photovoltaic systems: MPPT, current and voltage control", IEEE Trans. Ind. Informat., vol.8,no.2,pp.241-254, May, 2012.

- [6] S. B. Kjaer, J. K. Pedersen, and F. Blaabjerg, "A review of single-phase grid-connected inverters for photovoltaic modules," *IEEE Trans. Ind.Appl.*, vol. 41, no. 5, pp. 1292--1306, Sep./Oct. 2005.

- [7] S. B. Kjaer, J. K. Pedersen, and F. Blaabjerg, "A review of single-phase grid connected inverters for photovoltaic modules," *IEEE Trans. Ind. Appl.*, vol. 41, no. 5, pp. 1292–1306, Sep./Oct. 2005.

- [8] B. Singh, N. Mittal, K. S. Verma, "Multi-Level Inverter: A Literature Survey On Topologies And Control Strategies", International Journal of Reviews in Computing, Vol. 10, July 2012, pp. 1-16.

- [9] J. Rodriguez, J. S. Lai and F. Z. Peng, "Multilevel Inverters: Survey of Topologies, Controls, and Applications," IEEE Transactions on Industry Applications, vol. 49, no. 4, Aug. 2002, pp. 724-738.

- [10] Shunji Shi, Xiangzhou Wang, Shuhua Zheng, Yanxi Zhang, and Dongyuan Lu, "A New Diode-Clamped Multilevel Inverter with Balance Voltages of DC Capacitors", IEEE Transactions on Energy Conversion, Volume: 33, Issue: 4, Dec. 2018.

- [11] Liangzong He, Chen Cheng, "Flying-Capacitor-Clamped Five-Level Inverter Based on Bridge Modular Switched-Capacitor Topology", IEEE Transactions on Industrial Electronics, Volume: 63, Issue: 12, Dec. 2016.

- [12] Manoranjan Sahoo, Sivakumar Keerthipati, " A Three Level LC-Switching Based Voltage Boost

NPC Inverter", IEEE Transactions on Industrial Electronics , Volume: 64 , Issue: 4 , April 2017.

- [13] Gautam, S.; Gupta, R., "Switching Frequency Derivation for the Cascaded Multilevel Inverter Operating in Current Control Mode Using Multiband Hysteresis Modulation," IEEE Trans. on Power Electron., vol.29, no.3, pp.1480,1489, March 2014.

- [14] Tuhin S.Basu, Suman Maiti " A Hybrid Modular Multilevel Converter for Solar Power Integration," *IEEE Transactions on Industry Applications, DOI* 10.1109/TIA.2019.2928245, 2019.

- [15] Ataollah Mokhberdoran, Ali Ajami, "Symmetric and Asymmetric Design and Implementation of New Cascaded Multilevel Inverter Topology", IEEE Transactions on Power Electronics, Volume: 29, Issue: 12, Dec. 2014.

- [16] C. Dhanamjayulu and S. Meikandasivam, "Implementation and comparison of symmetric and asymmetric multilevel inverters for dynamic loads," IEEE Access, vol. 6, pp. 738–746, 2017.

- [17] E. A. Mahrous, N. A. Rahim, and W. P. Hew, "Three-phase three-level voltage source inverter with low switching frequency based on the twolevel inverter topology," IET Electric Power Appl., vol. 1, no. 4, pp.637–641, Jul. 2007.

- [18] Anil Kumar Yarlagadda, Vargil kumar Eate, Y.S.Kishore Babu, Abanishwar Chakraborti, "A Modified Seven Level Cascaded H Bridge Inverter", 5th IEEE Uttar Pradesh Section International Conference on Electrical, Electronics and Computer Engineering, 2018.

- [19] Sidharth sabyasachi, Raghavendra reddy, Santhosh kumar, Hiralal M.Suryawanshi, "Hybrid control Technique- Based Three Phase Cascaded Multilevel inverter Topology", *IEEE* Access Transactions, Vol. 5,2017, pp. 26912-26921. DOI 10.1109/ACCESS.2017.2727551.